The allowance for discretionary qudit levels facilitates a trade-off between the number of qudits in a quantum computer and the number of levels associated with each qudit [

6]. For instance, to transmit an

n-bit character in binary, ternary, and quaternary systems, the required number of input lines is $\lceil {{\mathrm{log}}}_{2}n\rceil $, $\lceil {{\mathrm{log}}}_{3}n\rceil $, and $\lceil {{\mathrm{log}}}_{4}n\rceil $, respectively. For a quantum system characterized by the level

d, the number of necessary input lines is $\lceil {{\mathrm{log}}}_{d}n\rceil $, which is approximately $1-{{\mathrm{log}}}_{d}2$, $1-{{\mathrm{log}}}_{d}3$, and $1-{{\mathrm{log}}}_{d}4$ times fewer than those required in binary, ternary, and quaternary systems. This characteristic allows for computations to be executed at a lower level, thereby resulting in enhanced execution speed [

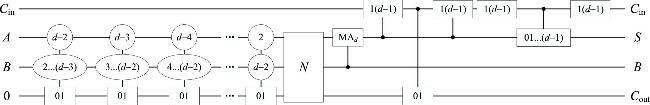

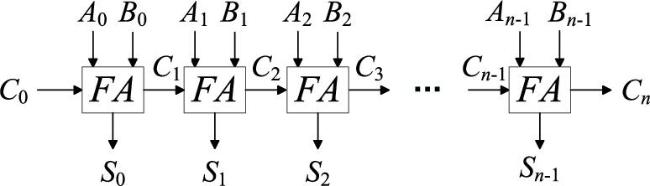

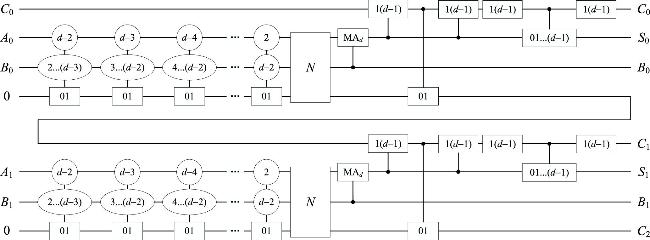

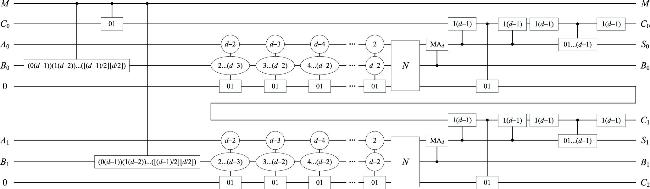

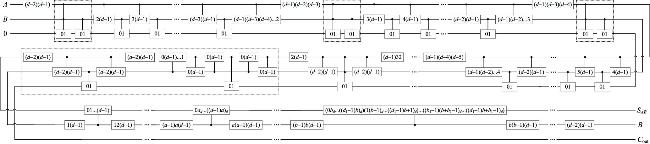

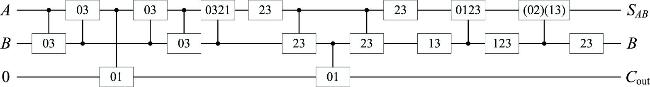

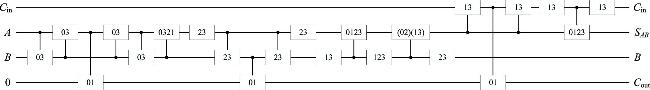

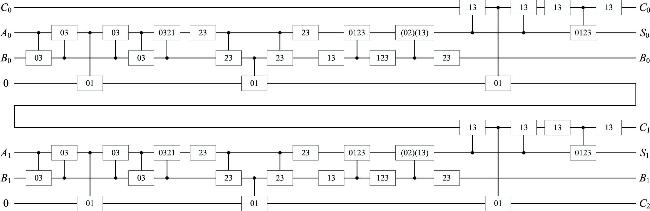

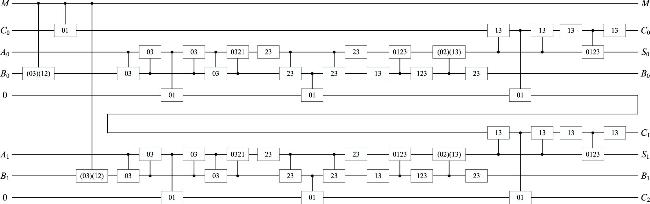

28]. The trade-off that can be used to simplify complex circuits is contingent upon the specific problems being addressed. It is crucial to realize fundamental components, such as quantum adders, that can be applied to different qudit levels. While most existing multi-valued quantum adder circuits have been primarily focused on ternary and quaternary systems, there is a notable scarcity of circuits developed for higher-valued quantum adders. Furthermore, many circuit design methodologies exhibit a lack of generalizability; for example, certain design approaches applicable to quaternary circuits may not extend to quinary circuits. In this paper, the top priority is the design of multi-valued quantum half-adder, full-adder, parallel adder, and parallel adder/subtractor circuits’ universal architectures, which are suitable for quaternary and higher-valued circuits. It is important to clarify that the term 'universal' here refers to the fact that any quaternary and higher-valued circuits can all be designed using the same design methodology, specifically through these architectures. Once the value of level

d is established, the corresponding multi-valued quantum adder circuits can be derived based on these architectures.